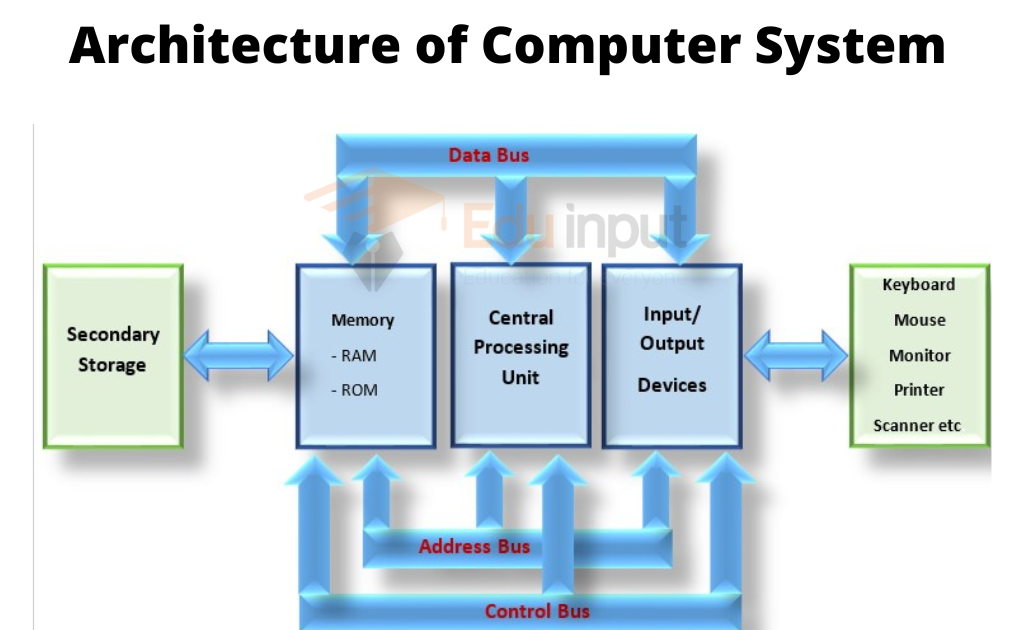

Von Neumann Architecture-Fetch, Decode, And Execute Cycle of CPU

Most modern processors work on the fetch-decode-execute principle. This is also called Von Neumann Architecture.

Von Neumann Architecture

When a set of instructions is to be executed, the instructions and data are loaded into the main memory. The address of the first instruction is copied into the program counter. The execution of an instruction by a processor is divided into three parts. These parts are Fetch, Decode, and Execute.

During the Fetch stage, the instruction register is loaded with the instruction’s address. The instruction fetch unit implements the instruction pointer. This instruction pointer is placed on the program counter. The instruction register is then loaded with the address of the instruction. This then allows the address to be fetched and loaded into the instruction register.

During the decode stage, the opcode, operand, and destination register are sent to the functional units. The opcode is decoded, and the necessary information is sent to the functional unit. During the Execute stage, the functional units carry out the actual execution of the instruction. This can involve addition, subtraction, shifts, calls, etc.

Fetch Instruction

In the first step, the processor fetches the instruction from the memory. The instruction is transferred from the memory to the instruction register.

In the following figure, the processor is ready to fetch instructions. The instruction pointer contains the address 0100. This value is placed on the address bus and a READ signal is issued on the control bus. The memory receives the signal and finds the contents memory location 0100. The memory location 0100 contains the instruction MOV AX, 0.

The memory places the instruction on the data bus. The processor then copies instructions from the data bus to the instruction register.

Decode Instruction

In this step, the instruction is decoded by the processor. The processor gets any operand if required by the instruction. For example, the instruction MOV AX, 0 stores the value 0 in the AX register. The processor will fetch the constant value 0 from the next location in the memory before executing the instruction.

In the above figure, the processor transfers the instruction from the instruction register to the decode unit. The instruction tells the computer to store 0 in the AX register. The decode unit now has all the details of how to do this.

Execute Instruction

In the last phase, the processor executes the instruction. It stores 0 in register AX.

The figure shows, that the processor executes the instruction MOV AX, 0. Finally, it adjusts the instruction pointer to point to the next instruction to be executed stored at address 0102.

written by

written by

Leave a Reply